電腦組成與體系結構:性能設計(英文版·原書第10版) | 運動資訊第一站 - 2024年7月

電腦組成與體系結構:性能設計(英文版·原書第10版)

本書以Intel x86體系結構和ARM兩個處理器系列為例,將當代電腦系統性能設計問題與計算機組成的基本概念和原理緊密聯繫起來,介紹了當代電腦體系結構的主流技術和近期新技術。

威廉·斯托林斯(William Stallings) 電腦圖書作者,曾13次獲得美國教材和學術專著作者協會頒發的年度最佳電腦科學教材獎。

目前,他是一名獨立顧問,為眾多電腦和網路製造商、軟體發展公司以及政府前沿研究機構提供服務。

第一部分 引言

第1章 基本概念和電腦演化1

1.1 組成與體系結構2

1.2 結構與功能3

1.3 電腦簡史11

1.4 Intel x86體系結構的演化27

1.5 嵌入式系統29

1.6 ARM體系結構33

1.7 雲計算39

1.8 關鍵字、複習題和練習題42

第2章 性能問題45

2.1 優化性能設計46

2.2 多核、MIC和GPGPU52

2.3 深刻理解性能的兩個定律:Ahmdahl定律和Little定律53

2.4 電腦性能的基本度量56

2.5 計算均值59

2.6 基準測試和SPEC67

2.7 關鍵字、複習題和練習題74

第二部分 電腦系統

第3章 電腦功能與互連的頂層視圖80

3.1 電腦元件81

3.2 電腦功能83

3.3 互連結構99

3.4 匯流排互連100

3.5 點對點互連102

3.6 PCI Express107

3.7 關鍵字、複習題和練習題116

第4章 快取記憶體120

4.1 電腦存儲系統概述121

4.2 快取記憶體記憶體原理128

4.3 快取記憶體設計要素131

4.4 Pentium 4 快取記憶體結構149

4.5 關鍵字、複習題和練習題152

附錄4A 兩級存儲的性能特徵157

第5章 內部記憶體165

5.1 半導體主存166

5.2 糾錯174

5.3 DDR DRAM180

5.4 快閃記憶體185

5.5 新的非易失性固態記憶體技術187

5.6 關鍵字、複習題和練習題190

第6章 外部記憶體194

6.1 磁片195

6.2 RAID204

6.3 固態硬碟212

6.4 光學記憶體217

6.5 磁帶222

6.6 關鍵字、複習題和練習題224

第7章 輸入/輸出228

7.1 外部設備230

7.2 I/O模組232

7.3 可程式設計I/O235

7.4 中斷驅動的I/O239

7.5 直接記憶體訪問248

7.6 直接快取記憶體訪問254

7.7 I/O通道和處理器261

7.8 外部互連標準263

7.9 IBM zEnterprise EC12 I/O系統266

7.10 關鍵字、複習題和練習題270

第8章 作業系統支援275

8.1 作業系統概述276

8.2 調度287

8.3 存儲管理293

8.4 Intel x86存儲管理304

8.5 ARM存儲管理309

8.6 關鍵字、複習題和練習題314

第三部分 算術與邏輯

第9章 數位系統318

9.1 十進位系統319

9.2 按位元記數系統320

9.3 二進位系統321

9.4 二進位與十進位的轉換321

9.5 十六進位表示324

9.6 關鍵字和練習題326

第10章 電腦算數運算328

10.1 算術與邏輯單元329

10.2 整數表示330

10.3 整數算數運算335

10.4 浮點表示350

10.5 浮點算數運算358

10.6 關鍵字、複習題和練習題367

第11章 數位邏輯372

11.1 布林代數373

11.2 門376

11.3 組合電路378

11.4 時序電路396

11.5 可程式設計邏輯裝置405

11.6 關鍵字和練習題409

第四部分 中央處理單元

第12章 指令集:特點與功能412

12.1 機器指令特點413

12.2 運算元類型420

12.3 Intel x86和ARM的資料類型422

12.4 操作類型425

12.5 Intel x86和ARM的操作類型438

12.6 關鍵字、複習題和練習題446

附錄12A 小端序、大端序和雙端序452

第13章 指令集:定址模式與格式456

13.1 定址模式457

13.2 x86和ARM的定址模式463

13.3 指令格式469

13.4 x86和ARM指令格式477

13.5 組合語言482

13.6 關鍵字、複習題和練習題484

第14章 處理器結構與功能488

14.1 處理器組成489

14.2 寄存器組成491

14.3 運算速度496

14.4 指令流水線500

14.5 x86處理器系列517

14.6 ARM處理器524

14.7 關鍵字、複習題和練習題530

第15章 精簡指令集電腦535

15.1 指令執行特性537

15.2 大寄存器檔的使用542

15.3 基於編譯器的寄存器優化547

15.4 精簡指令集架構549

15.5 RISC流水線555

15.6 MIPS R4000559

15.7 SPARC565

15.8 RISC與CISC之爭570

15.9 關鍵字、複習題和練習題571

第16章 指令級並行與超標量處理器575

16.1 概述576

16.2 設計問題581

16.3 Intel Core微架構591

16.4 ARM Cortex-A8596

16.5 ARM Cortex-M3604

16.6 關鍵字、複習題和練習題608

第五部分 並行結構

第17章 並行處理613

17.1 多處理器結構615

17.2 對稱多處理器617

17.3 快取記憶體一致性和MESI協議621

17.4 多執行緒和片上多處理器628

17.5 集群633

17.6 非均勻記憶體訪問640

17.7 雲計算643

17.8 關鍵字、複習題和練習題650

第18章 多核電腦656

18.1 硬體性能問題657

18.2 軟體性能問題660

18.3 多核結構665

18.4 異構多核結構667

18.5 Intel Core i7-990X676

18.6 ARM Cortex-A15 MPCore677

18.7 IBM zEnterprise EC12大型機682

18.8 關鍵字、複習題和練習題685

第19章 通用圖形處理單元688

19.1 CUDA基礎689

19.2 GPU與CPU691

19.3 GPU架構概述692

19.4 Intel的Gen8 GPU701

19.5 何時把GPU當作輔助處理器使用704

19.6 關鍵字和複習題706

第六部分 控制單元

第20章 控制單元操作707

20.1 微操作708

20.2 處理器的控制714

20.3 硬佈線實現724

20.4 關鍵字、複習題和練習題727

第21章 微程式控制729

21.1 基本概念730

21.2 微指令序列739

21.3 微指令執行745

21.4 TI 8800755

21.5 關鍵字、複習題和練習題766

附錄A 計算機組成與體系結構教學專案768

附錄B 組合語言與相關主題774

參考文獻800

統治NBA的王者訓練:NBA勇士王...

統治NBA的王者訓練:NBA勇士王... 超越重力:徒手肌力系統訓練&體操聖...

超越重力:徒手肌力系統訓練&體操聖... 1天4分鐘!持續燃脂12小時! 2...

1天4分鐘!持續燃脂12小時! 2... 在異世界獲得超強能力的我,在現實世...

在異世界獲得超強能力的我,在現實世... 天生是英雄

天生是英雄 越跑越勇敢:聖母峰馬拉松全紀錄

越跑越勇敢:聖母峰馬拉松全紀錄 超越重力:徒手肌力系統訓練&體操聖...

超越重力:徒手肌力系統訓練&體操聖... 街頭健身:倒三角、胸大肌、人魚線‧...

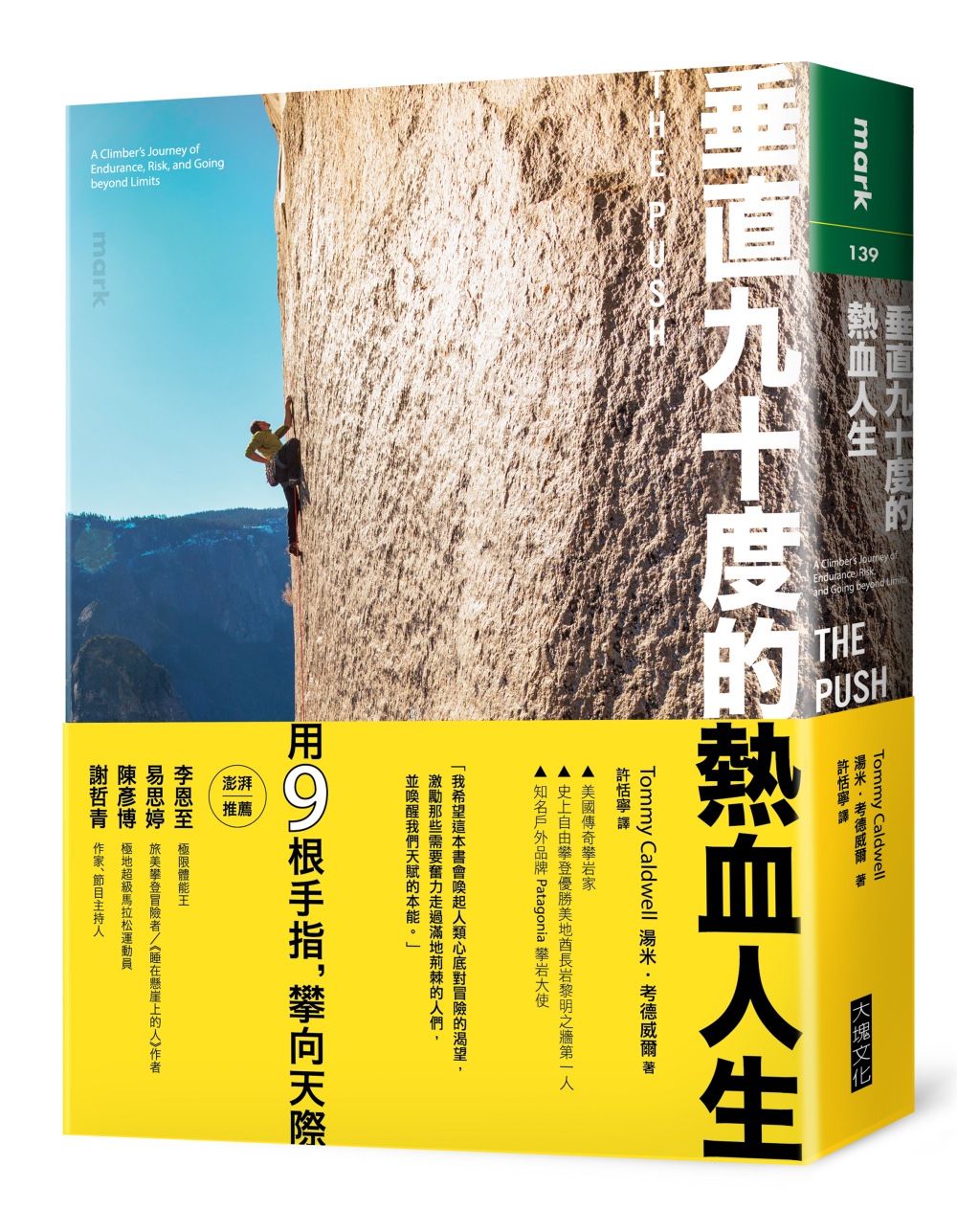

街頭健身:倒三角、胸大肌、人魚線‧... 垂直九十度的熱血人生

垂直九十度的熱血人生 吹鼓吹詩論壇三十二號:文字有氧 筋...

吹鼓吹詩論壇三十二號:文字有氧 筋...